Программа эксклюзивной разработки «Диполь» рассчитана на специалистов радиоэлектронной отрасли, связанных с производством печатных плат: инженеров и контролеров ОТК, технологов, операторов линии поверхностного монтажа, конструкторов, сотрудников входного контроля электронных компонентов.

Однодневный учебный курс состоит из теоретических и практических частей:

1. Теория - примеры дефектов, анализ причин их появления, обзор методов предупреждения.

Рассматриваются следующие вопросы:

-

общие сведения о технологии рентген-контроля;

-

дефекты монтажа электронных компонентов по типам корпусов (BGA, LGA, QFN, DFN) и методы их предупреждения;

-

дефекты изготовления печатных оснований;

-

входной контроль электронных компонентов и печатных плат;

-

прочие дефекты монтажа и методы их предупреждения.

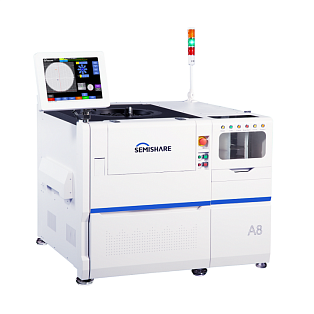

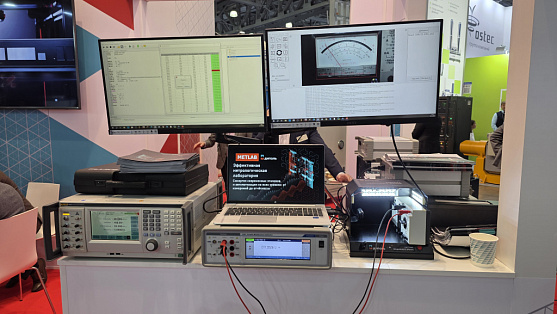

2. Практика – демонстрация алгоритмов и методов эффективной работы по поиску и анализу дефектов. Работа проводится на оборудовании (установке рентген-контроля) предприятия-заказчика.

Обучение проводится на тренировочных образцах, а также на образцах заказчика (печатные платы, электронные компоненты).

Требования к участникам

В состав учебной группы может входить не более пяти человек. Учащиеся должны иметь навыки работы с рентгеновским оборудованием. Тренинг платный.

Данный учебный курс включен в цикл образовательных мероприятий компании и проводится по мере комплектования групп на предприятии-заказчике.

Заявку на участие в тренинге «Поиск и анализ дефектов с помощью установки рентген-контроля» следует направлять по адресу info@dipaul.ru с пометкой "Тренинг"

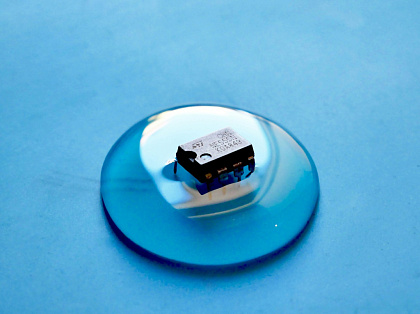

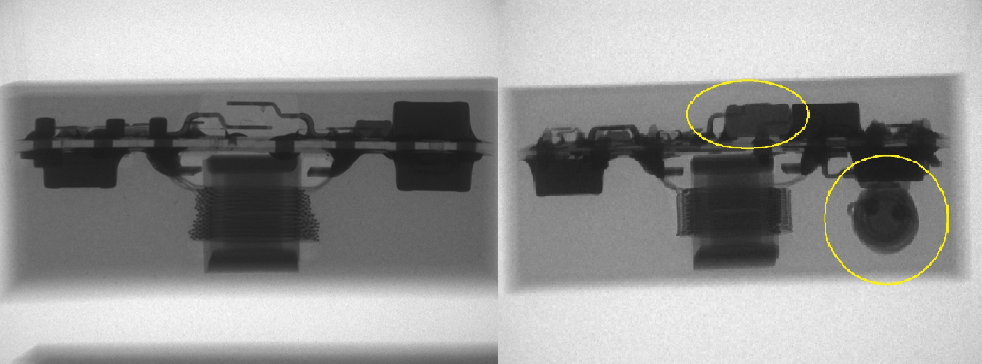

Рис.1. Отсутствие заполнения монтажных отверстий припоем

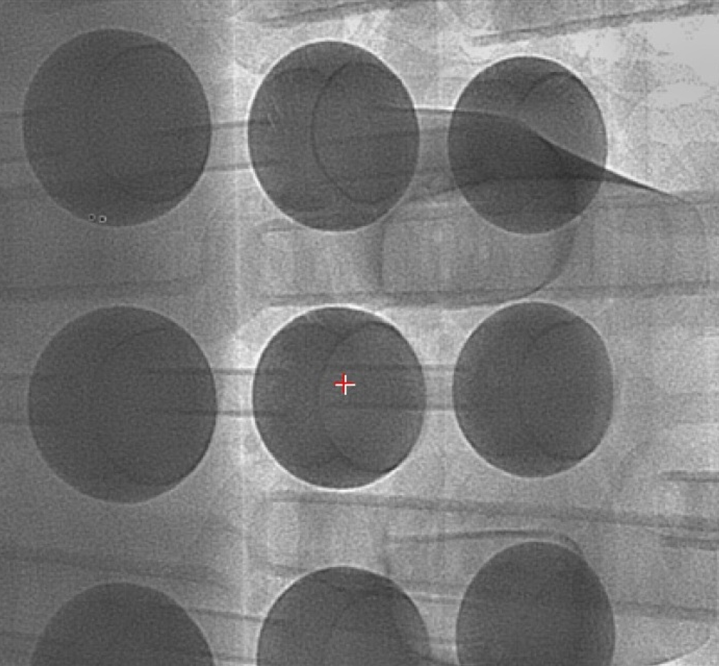

Рис.2. Контрафактный компонент

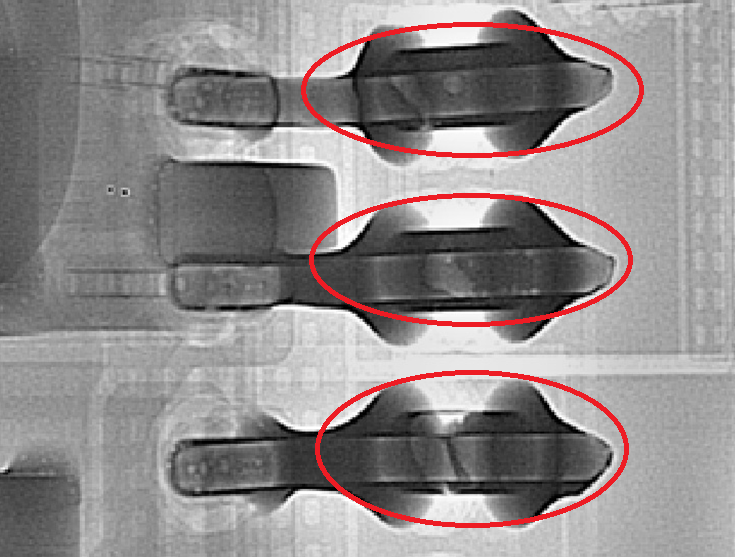

Рис.3. Недостаточное количество припоя в паяных соединениях микросхемы в корпусе BGA

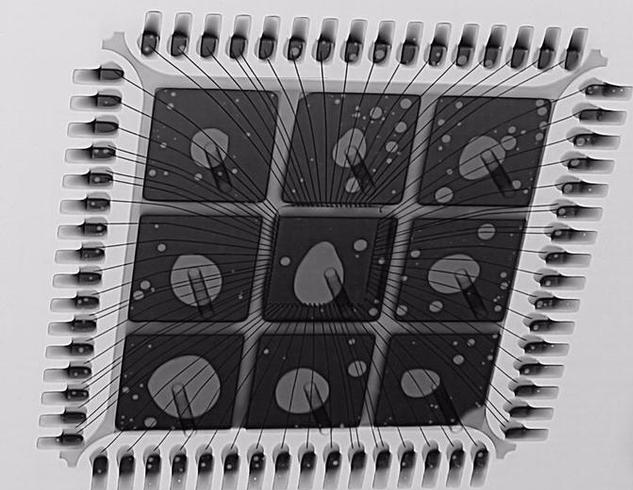

Рис.4. Хорошее смачивание контактных площадок микросхемы в корпусе BGA

Рис.5. Пустоты при пайке микросхемы в корпусе QFN